# Advanced Compiling Techniques to reduce RAM Usage of Static Operating Systems

Der Technischen Fakultät der Universität Erlangen-Nürnberg zur Erlangung des Grades

DOKTOR-INGENIEUR

vorgelegt von

Volker Barthelmann

Erlangen - 2004

# Als Dissertation genehmigt von der Technischen Fakultät der Universität Erlangen-Nürnberg

Tag der Einreichung: 07.01.2004 Tag der Promotion: 11.03.2004

Dekan: Prof. Dr. Albrecht Winnacker Berichterstatter: Prof. Dr. Michael Philippsen

Prof. Dr. Wolfgang Schröder-Preikschat

# Zusammenfassung

In den letzten Jahren wurde eine steigende Anzahl kleiner eingebetteter Systeme in hohen Stückzahlen eingesetzt. Beispielsweise in der Automobilindustrie, wo annähernd 100 elektronische Steuergeräte (ECUs) in einzelnen Oberklassefahrzeugen und bereits mehrere Dutzend in Mittelklassefahrzeugen verbaut werden. Meist werden kleine "System-on-Chip" Mikrocontroller mit statischen Betriebssystemen benutzt. Da das RAM auf diesen Chips sehr teuer ist und nur wenige KB davon auf solchen Systemen verfügbar sind, ist die Reduzierung des RAM-Verbrauchs ein wichtiger Punkt um Kosten zu senken — besonders bei der Produktion hoher Stückzahlen.

Diese Dissertation stellt einige neue Verfahren vor, um den RAM-Verbrauch solcher Systeme durch die Anwendung fortgeschrittener Übersetzungs- und Optimierungstechniken zu reduzieren. Klassische Optimierungen werden hinsichtlich ihrer Auswirkungen auf den RAM-Verbrauch untersucht. Durch geschickte Auswahl von Optimierungsalgorithmen kann der RAM-Verbrauch in einer Testreihe um fast 20% gesenkt werden. Obergrenzen für Stackgrößen der Tasks der Anwendung werden vom Übersetzer statisch berechnet. Durch modulübergreifende Analyse auf Hochsprachenebene werden hier gute Ergebnisse erreicht, die im Vergleich mit einem kommerziell verfügbaren Werkzeug Vorteile in der Handhabbarkeit und Zuverlässigkeit zeigen. Als wichtigster Punkt werden die Registersätze, die das Betriebssystem sichern muss, wenn ein Task unterbrochen wird, optimiert, indem vermieden wird, Register unnötig zu speichern. Registervergabe über Taskgrenzen hinweg reduziert den Speicherbedarf für diese Registersätze weiter.

Die neuen Algorithmen wurden in einen Übersetzer eingebaut und eine kommerzielle OSEK Implementierung wurde modifiziert, um die neuen Optimierungen zu nutzen. Tests auf echter Hardware, sowie Vergleiche mit kommerziellen Programmen zeigen nicht nur, dass das System funktioniert und sowohl Benutzbarkeit als auch Wartbarkeit verbessert, sondern auch, dass eine signifikante Reduzierung des RAM-Verbrauchs und der damit verbundenen Kosten möglich ist. In einer Reihe von Benchmarks wird der RAM-Verbrauch i.d.R. um 30%–60% gesenkt.

## Abstract

In recent years, a rapidly growing number of small embedded systems have been used in very high volumes. One example is the automotive industry, where the number of Electronic Control Units (ECU) in a single car is approaching 100 for high end automobiles and several dozens are used in mid-range cars. Small system-on-chip microcontrollers are often used with static operating systems. As on-chip RAM is rather expensive and only few KBs of RAM are available on such devices, reducing the RAM usage is an important objective in order to save costs — especially in high-volume production.

This thesis presents several new approaches to reduce the RAM usage of such systems by applying advanced compilation and optimization techniques. Common optimizations are examined regarding their impact on RAM usage. By selecting classical optimization algorithms regarding their impact on RAM usage, the RAM required for a series of test cases is reduced by almost 20%. Upper bounds for stack sizes of application tasks will be statically calculated using high-level analysis available in the compiler. Comparisons with a commercial tool working on machine-code-level show clear advantages regarding maintainability as well as reliability. Most important, the register sets stored by the operating system when a task is preempted are optimized by abstaining from saving unnecessary registers. Inter-task register-allocation further reduces the RAM required to save those task contexts.

The new algorithms have been added to a production quality compiler and a full commercial OSEK implementation was modified to make use of the new optimizations. Tests on real hardware as well as comparisons with commercial tools not only show that the system works and improves usability and maintainability, but also that significant reductions of RAM requirements, and therefore cost savings, are possible. In a series of benchmarks, RAM usage is reduced on average by 30%–60%.

# Contents

| 1 | Intr | $\operatorname{roduct}$ | ion                                      | 13 |

|---|------|-------------------------|------------------------------------------|----|

|   | 1.1  | Static                  | Operating Systems                        | 15 |

|   | 1.2  | Comp                    | oilers for Embedded Systems              | 16 |

|   | 1.3  | RAM                     | Usage                                    | 17 |

|   | 1.4  | Contr                   | ibutions and Organization of this Thesis | 17 |

| 2 | Tar  | get/Eı                  | nvironment                               | 19 |

|   | 2.1  | OSEK                    | Κ                                        | 19 |

|   |      | 2.1.1                   | Philosophy                               | 19 |

|   |      | 2.1.2                   | Portability                              | 20 |

|   |      | 2.1.3                   | OSEK Implementation Language             | 20 |

|   |      | 2.1.4                   | Task Management                          | 20 |

|   |      | 2.1.5                   | OSEK Events                              | 23 |

|   |      | 2.1.6                   | OSEK Resources                           | 23 |

|   |      | 2.1.7                   | Interrupt Service Routines               | 24 |

|   |      | 2.1.8                   | Properties of Application Code           | 24 |

|   | 2.2  | Exam                    | ples of relevant Microcontrollers        | 25 |

|   |      | 2.2.1                   | 68HC12/HCS12                             | 25 |

|   |      | 2.2.2                   | C16X/ST10                                | 26 |

|   |      | 2.2.3                   | MPC5XX                                   | 28 |

|   | 2.3  | The v                   | bcc Compiler                             | 29 |

|   |      | 2.3.1                   | General                                  | 29 |

|   |      | 2.3.2                   | Support for Embedded Systems             | 30 |

|   |      | 2.3.3                   | Optimizations                            | 32 |

|   |      | 2.3.4                   | Cross-Module Analysis                    | 33 |

| 3 | Cor  | nmon                    | Optimizations                            | 35 |

|   | 3.1  | Why                     | Optimizing?                              | 36 |

|   |      | 3.1.1                   | Disadvantages of Optimizing Compilers    | 36 |

|   |      | 3.1.2                   | Advantages of Optimizing Compilers       | 37 |

|   | 3.2  | Relate                  | ed Work                                  | 39 |

|   | 3.3  | Discus                  | ssion of selected Optimizations          | 39 |

|   |      | 3.3.1                   | Flow Optimizations                       | 39 |

|   |      | 3.3.2                   | Dead Assignment Elimination              | 40 |

|   |      | 3.3.3                   | Constant Propagation                     | 42 |

|   |      | 3.3.4                   | Common Subexpression Elimination         | 42 |

|   |      | 3.3.5                   | Copy Propagation                         | 45 |

|   |      | 3.3.6                   | Loop-Invariant Code Motion               | 46 |

|   |      | 3.3.7                   | Strength-Reduction                       | 48 |

|   |      | 3.3.8                   | Loop Unrolling                           | 50 |

8 CONTENTS

|          |     | 3.3.9  | Function Inlining                   | 52  |

|----------|-----|--------|-------------------------------------|-----|

|          |     | 3.3.10 | Register Allocation                 | 54  |

|          |     | 3.3.11 | Instruction Scheduling              | 55  |

|          |     |        | Alias Analysis                      |     |

|          |     | 3.3.13 | Inter-Procedural Data-Flow Analysis | 59  |

|          |     |        | Cross-Module Optimizations          | 61  |

|          | 3.4 |        | ination of Results                  | 64  |

|          | 3.5 |        | usion                               | 65  |

| 4        | Sta | ck Ana | dysis                               | 67  |

|          | 4.1 |        | ng practice and Related Work        | 68  |

|          |     | 4.1.1  | Guessing and Testing                | 68  |

|          |     | 4.1.2  | High-Water Marks                    |     |

|          |     | 4.1.3  | Manual Analysis                     |     |

|          |     | 4.1.4  | Traditional Compilers               |     |

|          |     | 4.1.5  | Post Link-Time Analyzers            |     |

|          |     | 4.1.6  | Further Related Work                |     |

|          |     | 4.1.7  | Example: AbsInt StackAnalyzer       |     |

|          | 4.2 |        | Level Approach                      |     |

|          | 4.2 | 4.2.1  | * *                                 |     |

|          |     |        | Goals                               |     |

|          |     | 4.2.2  | Implementation                      |     |

|          |     | 4.2.3  | Results and Comparison              | 92  |

| <b>5</b> | Con |        | Optimization                        | 111 |

|          | 5.1 |        | Contexts                            |     |

|          | 5.2 |        | nt Practice and Related Work        |     |

|          | 5.3 | Conte  | xt Optimization                     |     |

|          |     | 5.3.1  | Example                             | 114 |

|          |     | 5.3.2  | Bounding Task-Contexts              | 115 |

|          |     | 5.3.3  | Inter-Task Register-Allocation      | 116 |

|          | 5.4 | Requir | rements on Compilers                | 117 |

|          | 5.5 | Experi | imental Implementation and Results  | 118 |

| 6        | Rea | l OSE  | K Implementation                    | 121 |

|          | 6.1 |        | SEK                                 | 121 |

|          | 6.2 | Impler | mentation Details                   | 122 |

|          |     | 6.2.1  | Adaption of ProOSEK to vbcc         | 122 |

|          |     | 6.2.2  | Stack Analysis                      | 122 |

|          |     | 6.2.3  | Task Attributes                     |     |

|          |     | 6.2.4  | Calculation of Task Contexts        |     |

|          |     | 6.2.5  | Inter-Task Register-Allocation      |     |

|          |     | 6.2.6  | Generation of Stacks                |     |

|          |     | 6.2.7  | Context-Switch Code                 |     |

|          |     | 6.2.8  | System Calls and System Stack       |     |

|          |     | 6.2.9  | Interrupts                          |     |

|          | 6.3 |        | SS                                  |     |

|          | 0.0 | 6.3.1  | Task Constellations                 |     |

|          |     | 6.3.2  |                                     |     |

|          |     |        | 1                                   |     |

|          |     | 6.3.3  | Interior Lights                     | 131 |

133

7 Conclusion and Future Work

# List of Figures

| 1.1 | Die Overlay showing ROM and RAM sizes      | 14  |

|-----|--------------------------------------------|-----|

| 1.2 | Architecture of a Static Operating System  | 15  |

| 1.3 | New Architecture                           |     |

| 2.1 | OIL Example                                | 21  |

| 2.2 | OSEK OS Task-State Transitions             | 22  |

| 2.3 | OSEK OS preemptive Scheduling              | 22  |

| 2.4 | OSEK OS non-preemptive Scheduling          |     |

| 2.5 | OSEK Interrupt Handling                    |     |

| 2.6 | HC12 Register Set                          |     |

| 2.7 | C16X/ST10 Register Set                     |     |

| 2.8 | PowerPC Register Set                       |     |

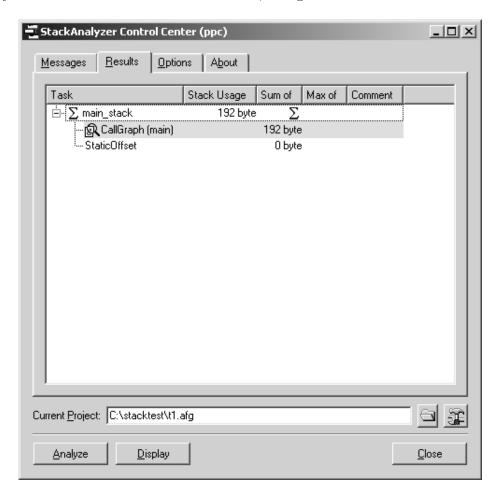

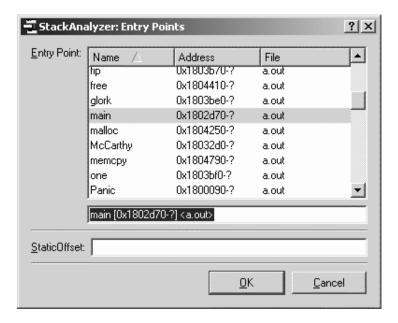

| 4.1 | StackAnalyzer ControlCenter                | 79  |

| 4.2 | StackAnalyzer Entry Point Selection Window |     |

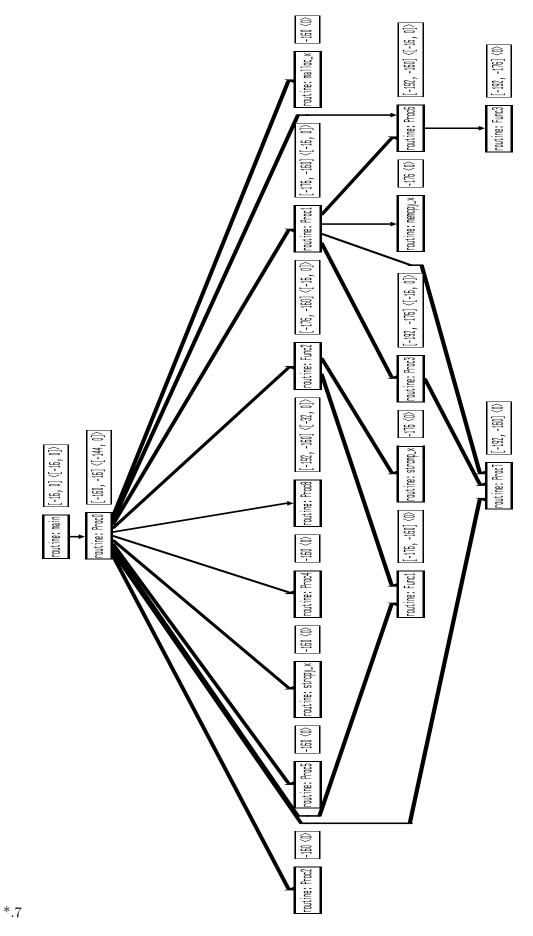

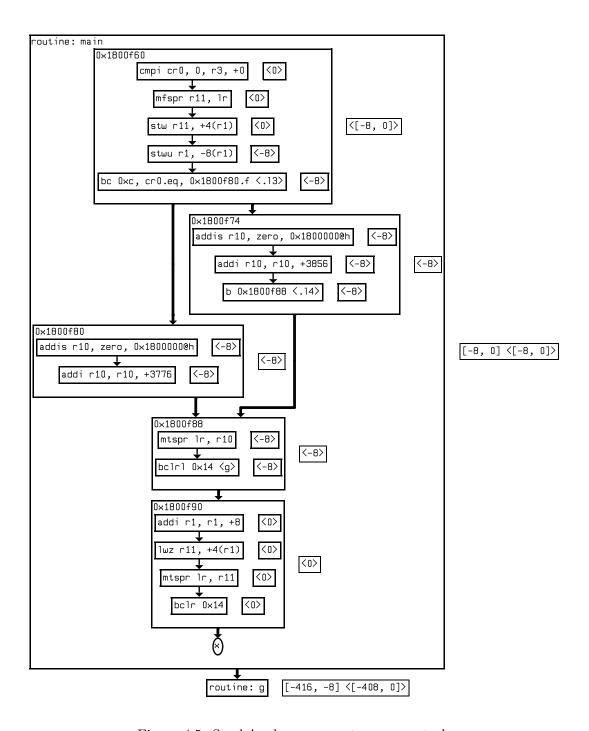

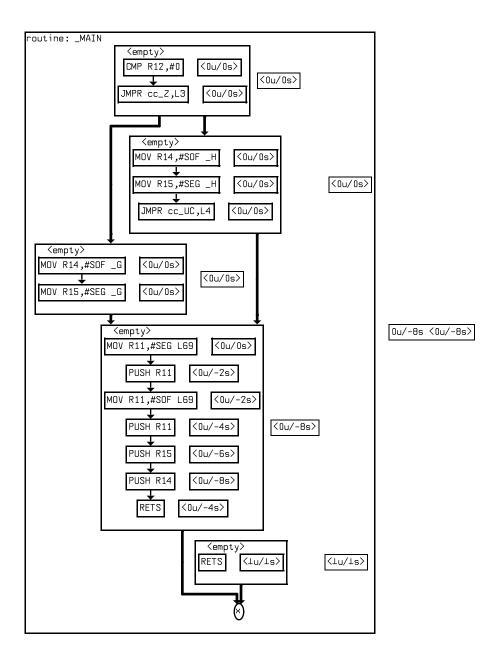

| 4.3 | Full Graph View                            | 83  |

| 4.4 | Zoom into Graph                            |     |

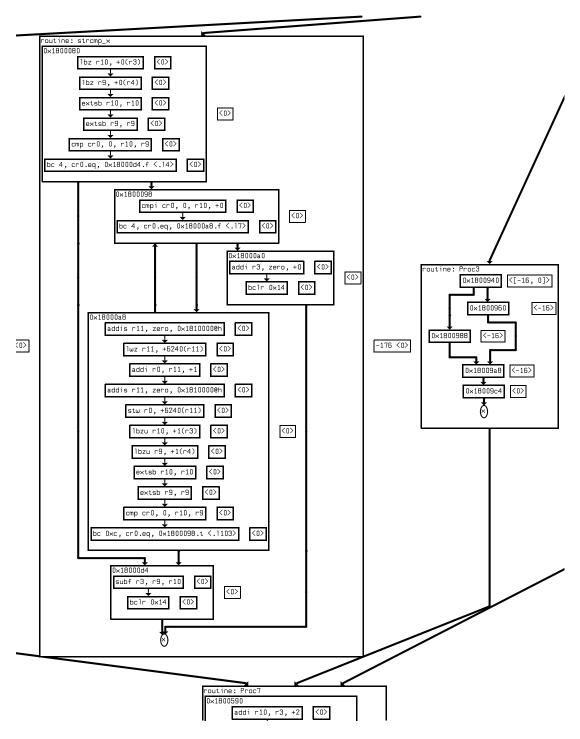

| 4.5 | StackAnalyzer computes wrong stack         |     |

| 4.6 | t8.c interpretation by StackAnalyzer       |     |

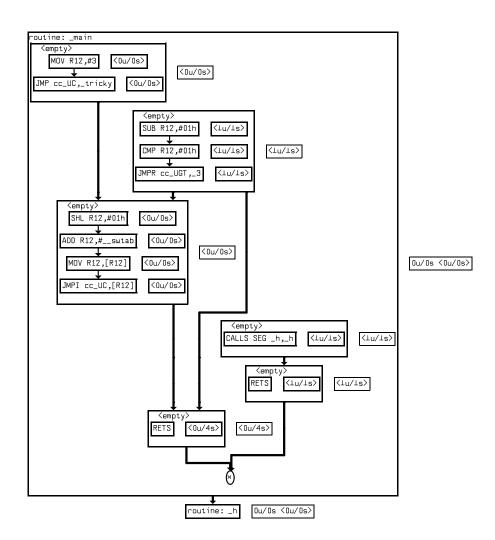

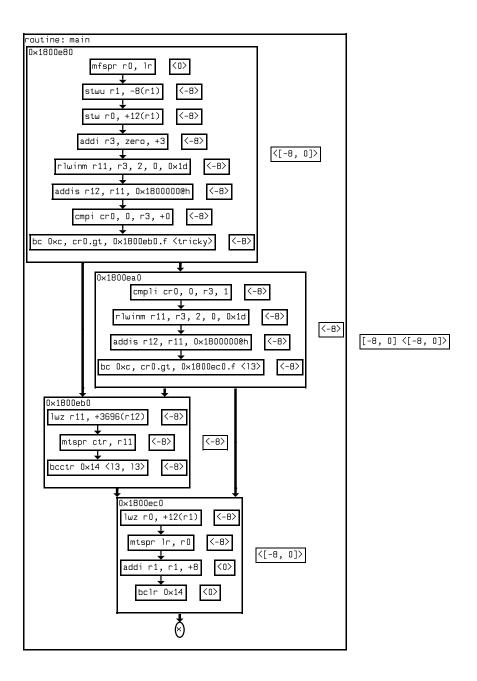

| 4.7 | Faked Switch Statement on C16X             |     |

| 4.8 | Faked Switch Statement on PowerPC          |     |

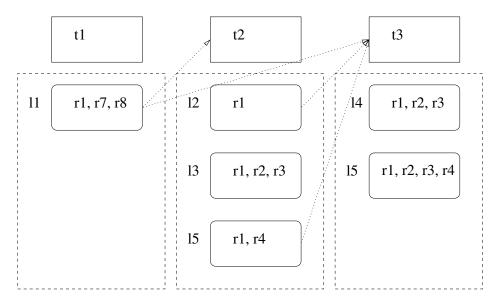

| 5.1 | Interference Graph                         | 115 |

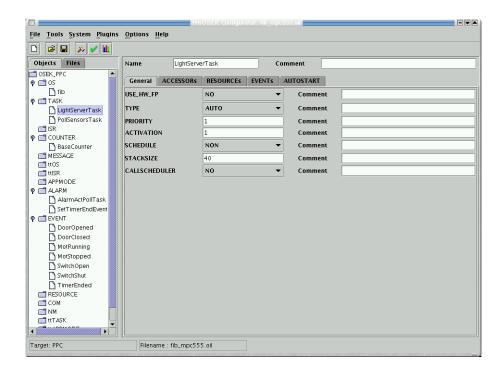

| 6.1 | ProOSEK Configurator                       | 199 |

10 LIST OF FIGURES

# List of Tables

| 2.1  | OSEK Task States                             |

|------|----------------------------------------------|

| 3.1  | Dead Assignment Elimination Results          |

| 3.2  | Constant Propagation Results                 |

| 3.3  | Common Subexpression Elimination Results     |

| 3.4  | Copy Propagation Results                     |

| 3.5  | Loop Invariant Code Motion Results           |

| 3.6  | Strength Reduction Results                   |

| 3.7  | Loop Unrolling Results                       |

| 3.8  | Function Inlining Results                    |

| 3.9  | Register Allocation Results                  |

| 3.10 | Inter-Procedural Register Allocation Results |

| 3.11 | Combined Results                             |

| 4.1  | Stack Analysis Results PowerPC               |

| 4.2  | Stack Analysis Results HC12                  |

| 4.3  | Stack Analysis Results C16X                  |

| 5.1  | Benchmark results                            |

| 6.1  | Benchmark results revisited                  |

| 6.2  | LED Example Results                          |

| 6.3  | Interior Lights Results 13                   |

12 LIST OF TABLES

## Chapter 1

## Introduction

In recent years, a rapidly growing number of small embedded systems have been used in very high volumes. One example is the automotive industry where the number of Electronic Control Units (ECU) in a single car is approaching 100 for high end automobiles and several dozen in mid-range cars (an overview of the ECUs in the current 7-series BMW is given in [68]; for numbers of microcontrollers in different cars, see [15]). Another domain is the emerging area of wearable computing which may produce very small systems in high volume.

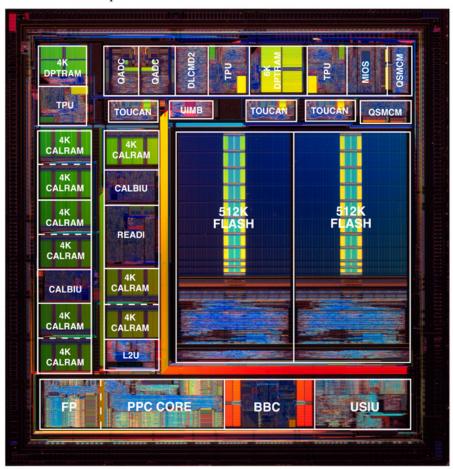

Typically system-on-chip microcontrollers are used which contain the CPU, peripherals, ROM and RAM on a single chip. ROM sizes of a few hundred KB and RAM sizes of a few KB are common. Figure 1.1 shows a die overlay of the MPC565, a microcontroller currently used in automotive applications. While the flash ROM with 1MB capacity clearly is the largest part of the chip, the blocks of RAM (which are only 4KB each) are the second biggest factor influencing die size, much bigger than, for example, the PowerPC core. When taking capacity into account, it can be observed that RAM takes up about ten times as much chip space compared to programmable flash ROM. This shows that reduction of RAM usage is an important goal. Even transformations that trade off RAM for ROM can still save die size unless about ten times as much additional ROM has to be traded for the RAM that is saved. Furthermore, off-the-shelf chips have a fixed amount of on-chip RAM and ROM. To fit an application into the chip, both ROM as well as RAM has to be sufficient (otherwise a larger and more expensive off-the-shelf chip has to be used). If there is not quite enough RAM space, but some unused ROM space, RAM reduction can help to fit the application on the smaller chip and save costs.

Not very long ago, these small systems were typically programmed in assembly language using no operating systems. In recent years, however, high level languages are often being used for such systems (see, for example, [93] or [135]) and the use of operating systems is getting more common. This is also illustrated by the fact that the market segment of 8bit microcontrollers in 2002 has shrunk by about 10%, whereas the segment of 32bit controllers (that are much better suited to e.g. C compilers) increased about 40% (16bit controllers stayed about equal), see [136], [137]. Also, new 8bit architectures are tailored to C programming, e.g. the Atmel AVR (see [9]). The current roadmap of Motorola [105], market leader for 8bit controllers, only shows future products for their HC08 series that has been optimized for C programs [136].

As, for example, the ECUs in cars are usually connected via several bus systems and have to co-operate, a common communication layer provided by the operating system is a big benefit. In addition, using the standard features of well-tested operating systems seems to promise more stable systems and shorten development times as application

## Motorola's MPC565 "Spanish Oak"

PowerPC<sup>TM</sup> Microprocessor

Figure 1.1: Die Overlay showing ROM and RAM sizes

programmers do not have to "re-invent the wheel".

Use of high level languages and operating systems also significantly reduces the amount of work necessary to port an application from one chip or architecture to another. Therefore, chips can be chosen more freely — an important benefit in volume production where every penny counts.

## 1.1 Static Operating Systems

Classic operating systems are not well suited for such systems because of several reasons. The most important of these being the high memory requirements. Another problem is the danger of fragmentation or memory leaks. Many ECUs are safety-critical and the risk of failure to allocate a system resource due to lack of RAM or memory fragmentation can not be tolerated.

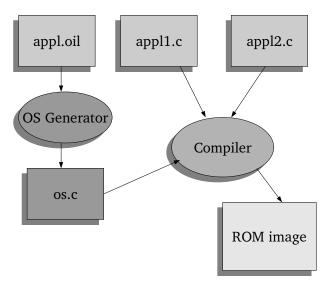

Static operating systems help to avoid these problems. In such operating systems all system resources like tasks, messages, mutexes etc. used by the application are configured statically using an offline tool. After verifying validity, a kernel which is specially optimized to this very application is generated from this configuration (see figure 1.2).

Figure 1.2: Architecture of a Static Operating System

All resources needed by the operating system are statically allocated during generation time and therefore no dynamic memory management is needed. Allocating an operating system resource can never fail!

As all resources used by the application are known when the kernel is generated, it is possible to produce a very small optimized kernel. Functionality not needed by this application can be automatically omitted, and the size of data structures can be reduced. For example, a task can be identified by a single byte that is used as an index into arrays containing the necessary information for all tasks. This is often more efficient than using a (larger) pointer to a task control block as is used in many systems.

Also, it allows the constant parts of the task control block to be placed into ROM. For very small systems, this can be important.

These benefits of static operating systems allow them to be used in very small systems (e.g. 8bit microcontrollers with 32KB ROM and 1KB RAM) and still leave enough room for the application.

The market of static operating systems is currently dominated by systems conforming to the OSEK specification [113] which will be described below.

## 1.2 Compilers for Embedded Systems

The way software for such systems is being developed has changed over the years. Traditionally, small systems that demand efficient and small code have been programmed almost exclusively in assembly language. The lack of compilers able to produce code that is sufficiently efficient was the main reason. Also, there are special requirements of such code (e.g. interrupt handlers, accessing special hardware etc.) that could not be expressed in high-level programming-languages.

Over time, compiler technology has improved. Many optimizations were built into compilers and — also an important point — the platforms used for developing (i.e. personal computers and workstations) have become powerful enough to run optimizing compilers with reasonable turn-around times.

Contrary to embedded systems, software development for larger systems has been done almost exclusively in high-level languages for a long time. With optimizing compilers becoming more common, assembly-language is being used less and less. Basically, compilers generate code that is "good enough" and there is no return of investment for writing code in assembly language.

However, the constraints for high-volume embedded systems are much tighter. Increased space requirements imply bigger hardware and higher costs. Therefore, there are much more cases where better optimizations allow significant cost reductions — which is an important reason why high-level languages were rarely used.

There are, however, good reasons for using high-level language compilers now. Software developers able to write good assembly code are rare — especially as every architecture has its own assembly language. Also, writing optimized assembly language code is usually more time-consuming and error-prone. As the complexity of embedded systems increases, assembly language becomes harder and harder to maintain. Also, as the market for embedded devices grows (see e.g. [87]), there is a growing demand for more and larger embedded software which has to be satisfied. The market size of embedded systems is about 100 times the desktop market and compilers for embedded systems will become more important according to [51].

Furthermore, code written in assembly language is tied to a certain architecture and usually can not be moved to another one without completely rewriting it. It is often necessary however to reduce costs by moving the application to another chip that is cheaper. With high volumes, the cost savings can be much higher than the cost of a recompilation. For assembly code, the cost of moving the application is much higher. Even if it is still lower than the savings that could be obtained by moving to another architecture, the time required to rewrite the code for the new system will rarely be acceptable.

As a result, there is a need for highly optimizing compilers that are able to generate very efficient code for such systems. Currently available compilers meet these constraints to varying degrees. Classical global optimizations are reasonably common

1.3. RAM USAGE

although there are a few (especially small and somewhat unusual) architectures that lack highly optimizing compilers.

There are countless research projects dealing with various aspects of compilation for embedded systems. The LANCE project [93] concentrates on retargetable code generation for DSPs, the SPAM project [130] examines very expensive optimizations to reduce hardware costs of embedded systems. Research on resource-aware compilation is described in [120]. The OPTIMIST project [111] examines integrated code generation for irregular architectures. Machine-independent optimizations and hardware-software co-design are researched in the OOPS project [112]. The SUIF [138] and Zephyr [153] projects offer frameworks for retargetable optimizing compilers. There are also many other academical and commercial compiling systems for embedded systems.

## 1.3 RAM Usage

The amount of RAM available on a small system-on-chip is very expensive and typically at least an order of magnitude smaller than on-chip ROM size (see section 2.2). Therefore, minimization of RAM usage is a very important objective — especially as optimizing for RAM usage seems somewhat neglected in existing compiler design.

Usage of RAM in a static system can usually be attributed to the following sources:

- static application data

- application stack

- static operating system data

- task contexts

Static application data can rarely be minimized unless the developer wrote code that contains unused data. Similarly, static operating system data is already minimized at generation time — one of the benefits of using static operating systems.

That leaves the application stacks and task contexts as major stack consumers. Task contexts contain the register sets the operating system must save when a task is preempted. Application stacks generally consist of the following items:

- local variables used by the task code

- register values pushed by the compiler

- temporary variables created by the compiler

- safety margins (if the stack size needed is not known exactly)

## 1.4 Contributions and Organization of this Thesis

This thesis presents several approaches to reduce RAM usage by applying new advanced compilation and optimization techniques. Chapter 2 introduces the environment that was used to implement and test these optimizations. The OSEK operating system is used as a static operating system. Some typical microcontrollers that are used in the automotive industry are presented, and an overview about vbcc, the compiler that was used as a basis to implement the new optimization algorithms, is given.

Following that, a series of classical compiler optimizations is discussed regarding the applicability to small embedded systems in chapter 3. Special attention is put on the

impact of those optimizations on RAM usage. Test results suggest that optimizing for RAM requires different compiler settings than optimizing for speed or code size. Therefore, an "optimize for RAM" option seems to be a promising extension of compilers for small embedded systems.

Chapter 4 on stack analysis describes a new approach to statically calculate the size of task stacks within the compiler to eliminate safety margins. Stack analysis was built into the compiler and comparing the results with a commercial post link-time tool shows the advantages of the high-level analysis performed.

Reducing the size of task contexts is the objective of chapter 5. The new idea is to compute optimized contexts for every task which contain only the registers that really have to be saved. Furthermore, the register allocation of the compiler is adapted to perform inter-task register-allocation. Experimental results show the theoretical improvements possible with this new optimization.

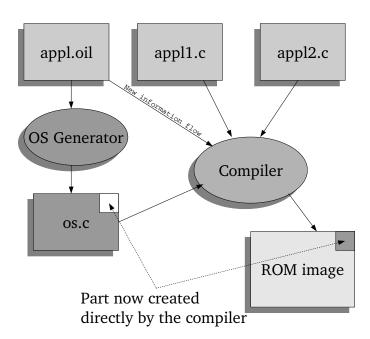

All these measures are then combined in a real world implementation in chapter 6. A commercial OSEK system is modified to work with the improved vbcc compiler. Context optimization and inter-task register-allocation is performed as well as stack analysis and some additional improvements. Generation of task stacks and task contexts is moved from the operating system generator to the compiler (see figure 1.3). Several problematic attributes like the stack size of tasks no longer have to be specified.

Figure 1.3: New Architecture

Tests on real hardware show not only that the system works and that the usability and maintainability is improved, but also that significant reductions in the RAM requirements are possible.

## Chapter 2

# Target/Environment

This chapter gives an overview of the target environment that is of interest in this thesis. A short introduction to OSEK OS, perhaps the most important static operating system, is given. Also, a few important microcontrollers that are used with OSEK in high-volume products are presented. Furthermore, the compiler that was used to implement the new optimizations that are proposed in this thesis is described shortly.

### 2.1 OSEK

The OSEK/VDX project defines an industry standard for an open software architecture for ECUs in vehicles. It is a result of harmonization between the German OSEK ("Offene Systeme und deren Schnittstellen für die Elektronik im Kraftfahrzeug" — Open systems and the corresponding interfaces for automotive electronics) and the French VDX ("Vehicle Distributed eXecutive"). Usually, just the term OSEK is used. OSEK is an open standard which is currently in the process of ISO standardisation (ISO 17356). OSEK is not a certain implementation but it specifies the behaviour and services of operating systems. Several vendors offer OSEK compliant operating systems, and ECUs running such OSEK implementations are used in production cars today. Currently, OSEK compliant operating systems from several companies have been officially certified [1, 144, 102, 95, 151, 57, 3]. Also, there are other commercial and academic implementations (e.g. [157, 133]).

OSEK/VDX consists of several specifications, including Operating System [114], Communication [118], Network Management [117], Time-Triggered Operating System [115], and others. This section will give a short overview of those parts of the OSEK Operating System specification which are relevant for this thesis. For full details, consult the OSEK specifications and the OSEK/VDX homepage [113].

## 2.1.1 Philosophy

The OSEK OS specification describes an API every OSEK compliant operating system has to implement. Only the behaviour is prescribed, the exact implementation, however, is up to the vendor. The main principles are:

- fully static system

- highly scalable

- portability of application code (source level only)

- configurable error checking

- support for running code from ROM

- only minimum hardware requirements must run on 8bit controllers

- predictable timing

The static configuration of the operating system is provided in a separate file, see section 2.1.3.

## 2.1.2 Portability

While portability on source level is desired, compromises have to be made here. Accessing hardware like on-chip peripherals is still done by the application. As very small systems are used on widely different hardware, a general hardware abstraction layer has been considered too expensive. It may be provided as an extension, but it is not required from the operating system.

## 2.1.3 OSEK Implementation Language

A standard file format called OIL (OSEK Implementation Language, see [116]) is used to specify the tasks, scheduling properties, and all other operating system resources used by the application. Note that this is the language to configure the static operating system parameters, not the language used to write the application code (this is usually done in C). Figure 2.1 shows part of an example OIL file that contains some global properties, a task description, as well as some OSEK events and resources (see below). Apart from standard attributes, an OIL file may contain additional vendor specific attributes that follow the syntax described in the OIL specification.

## 2.1.4 Task Management

OSEK tasks are the main threads of execution in a system. Although it is not explicitly stated, they share the same address space and there is no memory protection. OSEK does, however, discern between tasks that may enter a waiting state (called "extended tasks") and those that never do ("basic tasks"). This property has to be statically configured for each task to allow for a series of optimizations during generation of the operating system.

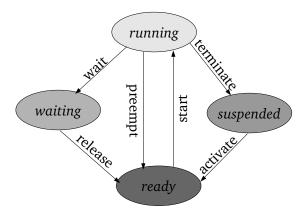

The control structures of each task can be statically allocated during system generation as there can only be one instance of every task. Basically, tasks can not be created, only activated. The possible task-states for an extended task are shown in table 2.1:

Table 2.1: OSEK Task States

| task-state | description                                                 |

|------------|-------------------------------------------------------------|

| running    | The CPU currently executes this task.                       |

| ready      | The task is ready to enter the running state,               |

|            | but another task is currently executing.                    |

| waiting    | A task is blocked because it requires an event (see below). |

| suspended  | The task is passive and has to be activated.                |

Figure 2.2 shows the possible task-state transitions of an extended task. For basic tasks, the waiting state and its edges do not exist.

2.1. OSEK 21

```

#include<PPC.oil>

CPU OSEK_PPC

OS ExampleOS

MICROCONTROLLER = MPC555;

CC = AUTO;

SCHEDULE = AUTO;

STATUS = EXTENDED;

STARTUPHOOK = FALSE;

ERRORHOOK = FALSE;

SHUTDOWNHOOK = FALSE;

PRETASKHOOK = FALSE;

POSTTASKHOOK = FALSE;

};

TASK ExampleTask

TYPE = AUTO;

AUTOSTART = FALSE;

SCHEDULE = FULL;

RESOURCE = Opener;

EVENT = WindowDown;

EVENT = WindowUp;

};

EVENT WindowUp;

EVENT WindowDown ;

RESOURCE Opener

RESOURCEPROPERTY = STANDARD;

};

};

```

Figure 2.1: OIL Example

Figure 2.2: OSEK OS Task-State Transitions

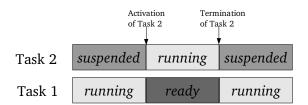

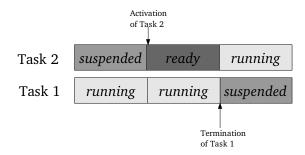

Every task has a statically assigned priority as well as an attribute specifying whether the task is fully preemptive or non-preemptive. A fully preemptive task is interrupted immediately when another task with higher priority gets ready (see figure 2.3 which assumes Task 2 has a higher priority). A non-preemptive task may only be interrupted when it voluntarily releases the CPU by invoking a system function like Schedule() (therefore, in figure 2.4, Task 1 keeps running even after Task 2 got ready).

Figure 2.3: OSEK OS preemptive Scheduling

In application code, each task is identified with the TASK keyword (a C macro defined in an operating system header file):

```

TASK(myTask)

{

...

TerminateTask();

}

```

Therefore, the code belonging to a task can be easily identified from the source code. While the tasks can have shared code (e.g. when calling the same function from the task body), each task has its own top-level function. Also, there can only be one instance of every task. Activation and termination of tasks is controlled by the following services:

• ActivateTask() moves a task from the *suspended* to the *ready* state.

2.1. OSEK 23

Figure 2.4: OSEK OS non-preemptive Scheduling

• TerminateTask() is used to terminate a task. A task can only terminate itself and must not terminate other tasks. A task must not return from its top-level function without calling TerminateTask().

#### 2.1.5 OSEK Events

Events are the OSEK equivalent of semaphores. They are objects statically defined in the OIL file. A task can wait on those events (waiting for several events at once is possible) it has been assigned in the OIL file. Tasks which are not assigned an event ("basic tasks") can never enter the *waiting* state. Setting of events can be done by every task. Every task has its own set of events, i.e. when a task sets an event, it has to specify for which task it is set (this allows sharing of bits in a mask of events). The most important system services related to events are:

- WaitEvent() puts a task in waiting state until one of the events it is waiting for is set (it will return immediately if one event is already set).

- SetEvent() sets an event for a task.

- ClearEvent() clears some of the events of the task calling this service.

## 2.1.6 OSEK Resources

OSEK Resources are mutexes used to implement controlled access to shared resources. To avoid the problems of deadlocks and especially priority inversion (for further information, see e.g. [24, 81]), OSEK implements a "priority ceiling" or "highest locker" protocol. All resource objects are statically assigned to tasks, i.e. any task that may want to obtain a resource must specify this fact in the OIL file. As soon as a task obtains a resource, its priority is raised to the highest priority of all tasks that may require that resource. The relevant system services of OSEK are:

- GetResource() obtains the specified resource and possibly increases the task's priority.

- ReleaseResource() releases the resource and resets the priority.

While occupying a resource, a task is not allowed to terminate itself or to wait for an event. As a result, a task will never be put into the waiting state when trying to obtain a resource — obtaining a resource will always succeed.

## 2.1.7 Interrupt Service Routines

Embedded systems usually do a lot of work that depends on external inputs, e.g. from sensors or busses. Interrupt service routines are used to handle such external events without the need for polling. As OSEK has to run on very small systems that may have to deal with high interrupt loads, efficiency is important here. Therefore, interrupt handlers in OSEK are very close to the hardware. There are even two general categories of ISRs (interrupt service routines) defined in OSEK:

- ISRs of category 1 are not allowed to call (almost all) system services.

- ISRs of category 2 may call several system services including ActivateTask() and SetEvent() which can cause rescheduling.

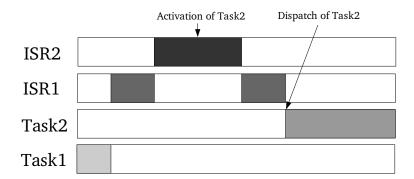

While ISRs of category 1 in general do not affect the operating system, category 2 ISRs usually have to be called in some special environment to allow rescheduling at the right point in time, i.e. just before returning from ISR level to task level. Figure 2.5 shows the right point in time to dispatch a task that has been activated by an ISR (assuming Task2 has a higher priority and Task1 is preemptive).

In the application code, those ISRs are written in a similar fashion to tasks:

```

ISR(myISR)

{

...

}

```

Figure 2.5: OSEK Interrupt Handling

### 2.1.8 Properties of Application Code

OSEK applications have certain properties that are very important for the work in this thesis, notably:

- no heap memory management

- no recursions

- use of libraries as source code rather than object code

- restricted use of function pointers

These restrictions are strongly suggested, for example, by the OSEK OS specification [113] or guidelines published by the Motor Industry Software Reliability Association [103]. As most automotive applications have real-time requirements and are often safety-critical, such constructs should be avoided. For example, recursions and heap memory management make it too difficult to verify that a system does not run out of space at some time. Use of function pointer variables is also considered dangerous. Availability of source code is required for scalability, certification, and portability.

For the compilation and analysis techniques presented in this thesis, these restrictions are crucial. They allow for much better static analysis than dynamic systems that make heavy use of, for example, recursions and heap memory management.

## 2.2 Examples of relevant Microcontrollers

The following sections will give a short overview of three microcontroller families that have been used for some experiments in this thesis (because of their widespread use in the automotive industry and support of the tools examined in this thesis, i.e. vbcc and StackAnalyzer). All of them are available in versions suitable for the automotive industry, i.e. as systems-on-chip with CPU, peripherals, RAM, and flash ROM on a single die. They are all supported by more than one commercial OSEK implementation and all of them are built into cars out on the road now.

## 2.2.1 68HC12/HCS12

The 68HC12 produced by Motorola is a small to medium 16bit architecture that has its roots in the old 6800 series of 8bit processors. Many derivates are available, offering different sets of peripherals and varying on-chip memory sizes. There is a line of derivates specially designed for automotive applications. A new, compatible product line, the HCS12 (or Star12) microcontrollers, show the continuing demand. A big field of application is body electronics in current cars (e.g. window openers, dashboard control, etc.).

The on-chip memory available on current 68HC12 devices ranges from 1KB RAM and 32KB of flash ROM up to 8KB of RAM and 128KB of ROM. The new HCS12 series ranges from 2KB RAM/64KB ROM up to 12KB RAM/256KB ROM. Unaligned memory access is allowed without any restrictions, therefore, eliminating the need for padding.

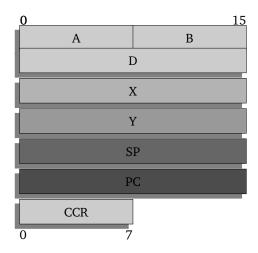

#### Register Set

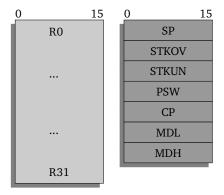

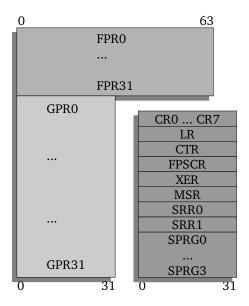

The 68HC12/HCS12 microcontrollers have a small register set that also shows the heritage of their 8bit ancestors. Two 8bit accumulator registers (A and B) can be used together as one 16bit accumulator (D) in many instructions. Additionally, there are two 16bit index registers (X and Y), a dedicated 16bit stack pointer (SP) as well as a program counter (PC). An 8bit flag register (CCR) stores condition codes and processor

state (see figure 2.6). Segment registers must be used to access the entire ROM area of the devices with larger flash memories (outside of 16bit address space).

Figure 2.6: HC12 Register Set

#### Instruction Set

The 68HC12/HCS12 provides instructions of varying length with many different kinds of memory operands available, e.g. absolute addressing, indexed addressing (via X, Y, or SP), double indirection, or pre- and post-increment/decrement addressing modes. As it is an accumulator architecture, most instructions use the accumulator as implicit operand and destination. Therefore, many instructions have a single operand or none at all.

Instructions do not have to be aligned in memory and, in fact, there are instructions occupying every length from a single byte up to six bytes. A so-called "instruction queue" is used to efficiently fetch instructions. No classic pipeline is used, however.

## 2.2.2 C16X/ST10

The C16X family of 16bit microcontrollers was originally developed by Siemens and various derivates are now produced by several manufacturers, most notably Infineon and ST Microelectronics (under the ST10 label). Many different configurations, varying peripherals as well as memory sizes are available. Typical automotive configurations from Infineon range from 2KB RAM/64KB ROM up to 8KB RAM/256KB ROM. ST Microelectronics offers devices up to 18KB RAM and 512KB ROM. Smaller configurations are used for body control in cars, but higher processing power makes them also suitable for more demanding applications. Classic implementations offer a four-stage pipeline, but improved versions with a five-stage pipeline are also now available.

## Register Set

The C16X architecture provides several windows of 16 16bit general purpose registers as well as a series of special purpose registers (see figure 2.7). The general purpose registers are not real core registers but they refer to locations in the internal RAM. A special register, the context-pointer CP, contains the start address of the register window in internal RAM that contains the general purpose registers. By changing

the context-pointer, the register window is moved. Basically, register Rn is a shortcut for the word at memory location  $CP + 2 \cdot n$ . For compilers and operating system, the following registers are of interest:

- SP: A dedicated stack pointer is available. Return addresses and interrupt frames are stored through this register. It can only address a limited part of internal RAM.

- STKOV/STKUN: These registers can be used for hardware monitoring of the internal stack. If the stack pointer leaves the window specified by those registers, an exception is raised.

- CP: With this context pointer, the window of general purpose registers can be moved around in the internal memory.

- PSW: The processor status word contains condition codes, interrupt levels etc.

- MDL/MDH: To reduce interrupt latency times, slow multiplication instructions can actually be preempted by interrupts. These registers store the state of the multiplication unit.

Figure 2.7: C16X/ST10 Register Set

To make use of more than 64KB of address space, segment registers must be used.

#### Instruction Set

All instructions on the C16X occupy either 16 or 32 bits and have to be aligned on word boundaries. Many instructions have two operands with one operand being both a source and destination. While in most cases one operand must be a general purpose register, the other one can also be a (real) memory operand or an immediate constant. Addressing modes include absolute addressing, indirect addressing via a general purpose register, and, in some cases, pre/post-increment/decrement modes.

As the dedicated stack pointer register is not usable in indexed addressing modes and can only address a part of internal RAM, a general purpose register is commonly used by compilers as a so called "user" stack pointer to address local variables etc.

### 2.2.3 MPC5XX

The Motorola MPC5XX family is a series of 32bit RISC microcontrollers designed for the automotive industry. They adhere to the PowerPC ISA (instruction set architecture) that has its roots in the IBM POWER architecture of high-end RISC processors for servers and workstations. There are also various other implementations of the PowerPC architecture made by other manufacturers [7, 74]. They range from microcontrollers to high-end server CPUs. The MPC5XX series is at the lower end of this range.

It is, however, on the higher end of microcontrollers currently using static operating systems. A big field of application is sophisticated engine management. Its high processing power (compared to the other microcontrollers described here) as well as some special peripheral support (e.g. programmable timer units) allow the ability to control high-revving engines with a larger amount of cylinders. Also, complex calculations required e.g. for knock detection can be implemented.

The on-chip memory sizes of current devices range from 26 KB RAM/448 KB ROM up to 36 KB RAM/1024 KB ROM.

### Register Set

The MPC5XX derivates have 32 64bit floating point registers, 32 32bit general purpose registers, an instruction pointer (32bit), and a series of (partially device-specific) special purpose registers (which can be transferred to/from general purpose registers but not directly to memory). This is illustrated in figure 2.8. The special purpose registers that are of interest for compilers and/or operating systems are:

- CRO-CR7: A 32bit register that stores 8 sets of 4bit condition codes.

- LR: When calling a subroutine, the return address is stored in this link register. Also, it can be used as the target of a computed call or jump.

- CTR: The special counter register can be used in some loop instructions or specify the target of a computed call or jump.

- FPSCR: Floating point status (e.g. rounding mode) is stored in this register.

- XER: Integer exception information is stored in this register.

- MSR: The machine state is stored in this register. It contains, for example, the interrupt enabling flag.

- SRR0/1: When servicing an exception, the CPU stores the old program counter and machine state register in those registers.

- SPRG0-3: These four registers are reserved for the operating system. They are needed, for example, to provide nested interrupt handlers.

#### Instruction Set and Execution Units

As a RISC architecture, all the PowerPC instructions occupy 32 bits. Most arithmetic instructions have three operands. Only registers and small immediate constants are available as operands. All accesses to memory have to be done via special load and store instructions. Addressing modes supported are indirect (through any general purpose register) with constant 16bit offset, register offset, or pre-increment/decrement modes.

Figure 2.8: PowerPC Register Set

All instructions have to be aligned (as well as memory accesses). An instruction cache is available and a four-stage pipeline allows single-cycle execution of many instructions. The CPU provides four execution units:

- The *integer unit* performs arithmetic operations on the general purpose registers, etc.

- Floating point operations are executed in the *floating point unit*.

- The *load/store unit* handles all accesses to memory.

- Changes in control flow are handled by the *branch unit* which supports, for example, static branch prediction.

The units can operate somewhat in parallel and also some out-of-order execution is possible. Nevertheless, the CPU appears fully sequential to the application. For example, zero-cycle branches are possible.

## 2.3 The vbcc Compiler

This section shall give a short overview of vbcc, a compiler that was written by the author of this thesis and is used as a basis for the work that is presented herein.

### 2.3.1 General

vbcc is a highly optimizing portable and retargetable ISO C compiler. It supports ISO C according to ISO/IEC 9899:1989 and a subset of the new standard ISO/IEC 9899:1999 (C99).

It is split into a target-independent and a target-dependent part, and provides complete abstraction of host- and target-arithmetic. Therefore, it fully supports cross-compiling for 8, 16, 32 and 64bit architectures.

The compiler itself is written in portable C and can be compiled and run on all common host operating systems like Linux, Unix, or Windows.

While it is not sold commercially at the moment, the compiler itself is not an academic research project but a production quality compiler that has been in real public use and has successfully translated large projects, including itself, as a search of the web or newsgroups for vbcc and compiler will reveal (see [54] for a visually appealing application using vbcc).

The compiler translates C files to assembly code (several backends exist). A frontend with Unix cc compatible options is provided that calls compiler, assembler, scheduler, and linker. This frontend is driven by a configuration file and enables support for different target systems or assembler/linker tool chains.

## 2.3.2 Support for Embedded Systems

When programming embedded systems, there can be several additional requirements for compilers. The next paragraphs will give a short description of what features are available in vbcc and how they are implemented.

## Target-Specific Extended Types

Obviously, in a retargetable compiler, the size and layout of standard data types must be controlled by the backend and also adhered to by the frontend. For example, the code

```

if(65535U + 1 == 0)

a();

else

b();

```

has to call a() on a target with 16bit int and b() on a target with 32bit int, no matter what size int is on the host.

This is not specific to embedded systems but rather to any retargetable compiler able to work as a cross-compiler. For many embedded architectures, however, further non-standard data-types are required.

As an example, many microcontrollers have special instructions supporting single bits. To make efficient use of them, bit types must be supported. Also, many 16bit controllers have segment registers that allow accessing more than 64KB of memory. However, as updating the segment registers for any memory access is very expensive, often code and/or data may be placed in special "near" sections which avoids updating of the segment registers. As a result, a pointer to such a "near" object may occupy one word and fit in a single register whereas a pointer to a "far" object requires two words and registers. A frequent case on small systems is to have short pointers to data and large pointers to functions.

vbcc allows backends to extend the type system of the frontend. This is used, for example, in the C16X/ST10 backend to provide different pointer sizes and a bit type.

#### Section Attributes

When programming an embedded system, some objects usually have to be placed in specific memory locations. For example, an interrupt service routine may have to be located at a specific address. vbcc provides an attribute that will put an object into a specified section (if supported by the backend and object format) which can then be located by the linker:

```

__section(".reset") reset_handler()

{

...

}

```

#### **Interrupt Handlers**

Interrupt service routines will be needed in almost every embedded system. While interrupt handlers for operating systems like Unix are mostly normal C functions that are called by the operating system, interrupt handlers for embedded systems are often directly called by the hardware.

As they are not called by a C function, there are other rules for these functions than the standard application binary interface (ABI). For example, returning from an interrupt is usually done with a different machine instruction than returning from a subroutine. Also, subroutines may destroy certain register contents as the calling function knows that they may be overwritten. However, an interrupt can preempt the running code at any time. Therefore an interrupt handler must not destroy any registers.

Special compiler support is needed to be able to write interrupt handlers in C rather than assembly language. If supported by the backend, vbcc provides a special attribute to designate an interrupt handler:

```

__interrupt isr_handler()

{

...

}

```

#### Inline Assembly

While most parts of an embedded system can usually be written in C, there are almost always some exceptions. For example, accessing a peripheral module on the microcontroller may require a special machine instruction the compiler does not emit (because it is not useful for standard C code).

Of course it is always possible to write a function in assembly language adhering to the ABI required by the compiler and call this code from C. However, this has some disadvantages:

- The ABI of the compiler may not be completely documented or hard to understand (e.g. rules for argument passing).

- Often, only a single machine instruction is needed. Creating an extra file to write an assembly function containing the instruction is tedious.

- Calling a separately assembled function will incur some overhead of execution time, code space, and RAM (return address).

- A function unknown to the compiler will be called and may cause significantly worse code generation. For example, the compiler may have to assume that the function destroys register contents or some variables.

To overcome these problems, many compilers provide some facility to include inline assembly code inside the C source. Usually this code is pasted more or less directly

into the output generated by the compiler. What is common amongst most compilers is that they do not parse or understand the inline assembly code and they assume that it behaves similar to a function call (e.g. jumping from one piece of inline assembly to another one and returning there will confuse most compilers). The syntax differs widely among different compilers as well as some of the following interesting points:

- Is there a way to pass arguments to the assembly code?

- Can assembly code use some temporary registers without risk that they might collide with registers used to pass arguments?

- What optimizations can the compiler do to the inline assembly code (e.g. function unrolling)?

- Does the compiler assume worst-case side-effects or is it possible to specify the side-effects caused by the inline assembly?

vbcc provides inline assembly through an extended syntax for function declarations. Internally, inline assembly is handled like a function call in vbcc. This automatically allows special features available for functions to be applied to inline assembly without the need for extra work. For example, the following declaration specifies an inline assembly function sin which uses only register fp0 (\_\_regsused("fp0")) and receives its argument in register fp0. Furthermore, the assembly code to insert is "fsin fp0".

\_\_regsused("fp0") double

$$sin(\_reg("fp0") x)="_

ufsin_

ufp0";$$

## 2.3.3 Optimizations

vbcc performs a series of classical optimizations. Data-flow analysis is performed. The following list shows the most important optimizations that are performed:

- cross-module function-inlining

- partial inlining of recursive functions

- inter-procedural data-flow analysis

- inter-procedural register-allocation

- register-allocation for global variables

- global common-subexpression-elimination

- global constant-propagation

- global copy-propagation

- dead-code-elimination

- alias-analysis

- loop-unrolling

- induction-variable elimination

- loop-invariant code-motion

- loop-reversal

## 2.3.4 Cross-Module Analysis

The new optimizations presented in this thesis require analysis of an entire application or at least an entire task. As the source code for tasks in embedded systems often is spread across several modules (source files), a compiler must not restrict its scope to single files to implement these optimizations.

vbcc is able to read in several source files at once and analyze and translate them as if the entire source code is contained in just one file. Its internal data structures allow it, for example, to discern between two static variables of the same name if they come from different source files.

Many projects, however, are built on makefiles that expect separate compilation. For example a makefile for a simple project consisting of two source files t1.c and t2.c could look like this:

```

t1.o: t1.c

$(CC) $(CCOPTS) -c -o t1.o t1.c

t2.o: t2.c

$(CC) $(CCOPTS) -c -o t2.o t2.c

test: t1.o t2.o

$(LD) $(LDOPTS) -o test t1.o t2.o

```

Such a procedure is also supported by using the frontend of vbcc. If a high optimization level is specified for the frontend of vbcc, it will pass an option to vbcc, telling it not to generate a normal object file. Instead vbcc will create a pseudo object file that retains enough information from the source file to delay analysis and optimization to some point later in time.

In the linking phase, the frontend will detect these pseudo objects and, instead of passing them directly to the linker, will call vbcc once again with all the pseudo objects to be linked at once. vbcc will optimize and translate them and the resulting object will be linked together with all the "normal" objects to produce the final executable. Similar schemes are used by other compilers, e.g. [128].

The makefiles will still work although every call of make will basically result in a complete rebuild as all the real work is now done in the linking phase which is always executed. However, with this mechanism switching from normal (and fast) separate compilation to cross-module optimization can be done just by changing the optimization settings for the frontend. There are only minor restrictions, e.g. it is not possible to use different options for each module as they are translated together.

## Chapter 3

# **Common Optimizations**

In this chapter, common standard optimizations available in current compilers and frequently presented in textbooks and scientific papers are discussed. After an introduction which discusses the usefulness of optimizing compilers in general, a series of typical optimizations performed by optimizing compilers are presented.

Many of the typical optimizations have been developed for personal computers, workstations and servers. In fact, most of the scientific research in the area of compiler optimizations has targeted such machines — issues like code-size or memory requirements of the generated code have only recently gained attention once more. Therefore, the question of whether the optimizations discussed are also recommendable for small embedded systems is examined (mostly they are) and which of them are suitable to reduce RAM requirements. The results suggest that optimizing for RAM usage needs new combinations of optimizations, different from those suitable for optimizing for speed or code size.

#### Impact of Optimizations on RAM Usage

Most current compilers optimize for execution speed and/or code size. While reducing code size was an important issue in the early years of compiler technology, with the introduction of microcomputers, focus in research of compiler optimizations has mostly been on execution speed [141]. This is reasonable, as most compiler research has been targeted at personal computers or larger systems where code size rarely matters. However, larger code can cause slower execution, e.g. due to cache misses, in many cases. In fact, many optimizations to improve execution speed also reduce code size.

Optimizing code size and execution speed are the classical objectives of optimization. For the small embedded systems addressed in this thesis, however, it has been shown in the previous chapters that there is an additional objective, namely RAM size. There are obvious reasons why RAM usage has not been addressed in research of compiler optimizations. Typical optimizations will change the use of RAM only slightly by introducing or removing (usually scalar) variables. On any but the smallest systems, these effects can be neglected as RAM usage is dominated either by code size (if code is loaded into RAM as it is done in most larger systems) or user data structures (which are typically not modified by common optimizations). On a system with only 2KB of RAM, however, a few bytes more can make a difference.

## 3.1 Why Optimizing?

Quality of generated code has been an issue since the early days of compiler construction. It was not long before it was proposed to carry out optimizing transformations automatically (see [108]). In the 1960s, smaller optimizations were included in compilers [152] and the first heavily optimizing compilers were produced, e.g. the Fortran H compiler (see [97]). Since then, much research into compiler optimizations has been carried out (e.g. [4, 83]). Today, there are still many conferences dealing with compiler optimizations, e.g. the "International symposium on Code generation and optimization" or, in the area of embedded systems, "Languages, Compilers and Tools for Embedded Systems" (LCTES), the "International conference on Compilers, architecture, and synthesis for embedded systems" (CASES) or the "International Workshop on Software and Compilers for Embedded Systems" (SCOPES). Among the targets of research are better support for new architectures and languages, or increasing the scope of optimizations.

As the computing power of microprocessors has been increasing very fast over the years, the usefulness of optimizing compilers is questioned regularly. At first sight, it is understandable as optimizing compilers inherently incorporate a number of disadvantages compared to their non-optimizing counterparts.

## 3.1.1 Disadvantages of Optimizing Compilers

The first apparent disadvantage optimizing compilers have are probably the much larger compilation times and memory requirements. While non-optimizing compilers will on average usually have linear complexity in time and space, optimizing compilers rarely do better than quadratic — often with even higher theoretical worst-case complexity in time. Faster compilation times are only possible for some languages and only with restrictions to the optimizations performed (see [23]).

Maybe the second most obvious problem for the user of the compiler will be the restrictions when debugging. Most compiler/debugger combinations offer either only very limited optimizations when debugging information is selected, or the debugger may display very confusing results.

One problem here is that most standard formats for debug information have been designed with simple compilers in mind. For example, they only support very simple expressions for locating variable values (e.g. constant offset to a frame-pointer register). In an optimizing compiler, however, a variable might be in a register at some part of the code, another register in other parts and reachable via changing offsets to a stack-pointer at yet another part of the code.

These shortcomings can be eliminated by sophisticated formats for debug information and (this is not always the case) debuggers that support it. For example, the DWARF2 format (see [140]) offers a reasonable variety of possibilities that support debugging code produced by optimizing compilers. Unfortunately, it is a pretty complex specification and most debuggers seem to support only a part of the functionality that is specified.

So, while some problems with debugging could be solved, there are others that simply can not be eliminated with the user interface of current source-level debuggers. For example, if variables or assignments have been removed or combined, there is no way the debugger can show the right value of a variable at some locations. In the following example, an optimizing compiler might just increment the parameter  $\mathbf{x}$  (e.g. if it is passed in a register) and return it.

```

int f(int x)

{

int y = x + 1;

return y;

}

```

As a result, neither of the two variables x and y would be displayed correctly over the function body. There are, of course, special cases where it would be possible to give the debugger information that would enable it to calculate the correct value of a variable that has been eliminated. For example, the value of an induction variable that has been eliminated by strength-reduction (see section 3.3.7) could be calculated from a pointer variable that has been introduced by the optimizer. In the general case, however, this is not possible.

Also, single stepping through the source code or setting break-points on source lines presents problems. Often machine instructions correspond to several source lines after instruction combining or machine instructions corresponding to different source lines are intermixed by instruction scheduling. Many optimizations destroy the one-to-one mapping of sequences of machine instructions to source lines. If this mapping is destroyed, neither single-stepping nor breaking at certain source-lines can work as expected.

The previous paragraphs explained some problems for the users of optimizing compilers. Another group of problems affect the developers writing the compilers and therefore development cost and stability of compilers.

Optimizing compilers are much more complicated and error-prone than simple non-optimizing compilers. They use a wide range of different algorithms (e.g. data-flow algorithms, pattern-matching, dynamic-programming, sorting, searching, etc.) and complex data-structures (e.g. trees, directed acyclic graphs, control-flow graphs, bit-vectors, hash-tables, lists, etc.).

Often different algorithms work sequentially or even interconnected on the same data-structures and pass information to each other. Therefore, bugs in an optimizing compiler may show up in a different part of the compiler (e.g. a wrongly propagated constant may be the result of corrupt data-flow information which may, in turn, be the result of a bug in the alias-analysis algorithm).

Additionally, the global analysis in optimizing compilers often causes bugs to appear at different parts of the translated program. For example, corrupt data-flow analysis at the end of a loop may be the cause for an incorrectly translated statement at the head of the loop. Furthermore, it is much harder to produce a small code snippet that reproduces a bug. Adding statements (like printing debugging output) as well as removing parts of code (to reduce the code to a minimum which is easier to check) may cause changes to the generated code at locations far away.

To sum it up, the steps in isolating and fixing an optimizer bug are usually much more complicated and not at all straight-forward like they are in a simple non-optimizing compiler.

## 3.1.2 Advantages of Optimizing Compilers

So now we have seen a series of disadvantages of optimizing compilers. Their main advantages obviously are speed and/or size of the generated code. Therefore, the justification of sophisticated optimizations depends on the importance of code quality. If the additional efficiency delivered through extensive optimization is not needed, optimizing compilers should better be avoided.

The major point to support this criticism is the fast increase of computing power. As a counterpart to "Moore's Law" which basically states that computing power doubles every 18 months due to advances in hardware technology, Proebsting postulates that improvements in compiler optimizations double computing power every 18 years [123]. While this is of course more a provocative anecdote than hard research, the basic tendency surely is correct. The impact of compiler optimizations has not nearly increased computing power as much as new hardware did. In fact, new optimizations often tend to improve the generated code less than previous optimizations did. If current compilers already generate code that is close to optimal then there is little room for improvement. So it is clear that new compiler optimizations have not and will not cause exponential improvements like hardware technology has done in the past.

On first sight, for many of today's applications, advanced optimizations indeed seem unnecessary. This is especially true if you are mostly familiar with typical personal computers and the most common applications like word processors, spreadsheets, etc. In this area it can be observed that even current low-end personal computers are powerful enough to deal with such applications. More so, the number of bugs observed in such applications strengthens the assumption that the ease of use of development tools and the speed of the development cycle is much more beneficial than optimization algorithms.

On the other hand, one has to keep in mind that there are other applications and other target domains that may have completely different requirements. Even on standard personal computers there are highly speed-critical applications like games or multimedia programs. Similarly, scientific number crunchers always can make use of as much computing power as is given to them (see [18]).

Of course the system-on-chip microcontrollers which are the main subject in this thesis also fall into this category. Here, larger memory footprints almost directly influence hardware costs by requiring larger on-chip memories or perhaps even off-chip memory including glue logic.

Similarly, slower code often adds to costs. If the code is too slow to guarantee the required real-time behaviour, a faster chip may have to be selected. This may become especially problematic as higher clock-speeds usually imply more power consumption and a higher sensitivity to electro-magnetic interference.

Even if the chosen chip is able to execute the non-optimized code fast enough to satisfy all real-time constraints, the optimized code may still need less power as it finishes the work in less time and therefore spends more time in idle or power-saving mode. In many embedded applications, power-consumption is a serious issue and therefore optimizations are desired.

As the next bigger chip may cost a few Euros more, the non-optimized code may cost millions of Euros in high-volume production if it forces the switch to a bigger chip. Or, equivalently, optimizations may save millions if they enable the application to use a cheaper microcontroller. As many production compilers are usually used to compile at least a few of such applications, this gives an estimation of how much effort might be justified to be put into an optimizing compiler.

So we have seen that compiler optimizations are still a topic of significant interest and of much practical use. In fact, the question of the purpose of optimizing compilers has been put up many years before when computing power was some orders of magnitude smaller than what is now considered suitable [141]. Actually, the topic is brought up regularly, see, for example, [59]. All these discussions have not changed the fact that these days the average level of available optimizations in production compilers has significantly and constantly increased over the years.

## 3.2 Related Work

Optimizing for code space has been an important topic in early compilers (see e.g. [97]) and has become an active topic of research again, especially for embedded systems. New approaches are, for example, presented in [10] or [44]. The problem of "over optimization", i.e. overly aggressive application of transformations resulting in degraded performance is mentioned, for example, in [11]. Methods to reduce register pressure are presented in [84]. However, these papers only consider the impact on execution speed. Similarly, many optimizations to improve cache performance have been discussed (see, for example, [101, 154]). A framework to examine the impact of optimizations on cache behaviour of embedded applications is presented in [156]. Reducing the power consumption of embedded systems by compiler optimizations has also become an active topic of research (see, for example, [155]). However, optimizing for power consumption is almost always identical to optimizing for execution speed as is shown in [35]. An overview of current works dealing with memory optimization techniques for embedded systems is presented in [121].

## 3.3 Discussion of selected Optimizations

Below, a selected list of probably the most used and frequently applied optimizations is reviewed regarding their applicability for small embedded systems, especially their impact on RAM usage. Code examples are usually written in C as the C language allows the effect of most optimizations to be expressed in source code. Note however, that some of these cases would rarely occur in code written by the programmer, but rather in intermediate code, possibly after other optimizations have already been performed.

After introducing each optimization, some comments on their implementation in vbcc will be given. The impact of several optimizations on RAM usage is measured using the 21 parts of the C torture test (cq.c) that is described in section 4.2.3. When evaluating a certain optimization, the corresponding transformation has been turned off and the results are compared to those obtained with vbcc default settings (marked "Ref.") on highest optimization level (unless mentioned otherwise). These default settings activate all optimizations apart from the most aggressive version of loop unrolling (see section 3.3.8). Therefore, the reference is usually with the optimization on. While this may be confusing at first, it allows the use of the same reference for all tests.

The first table (3.1) includes all test cases (with the RAM usage of each test case in bytes computed by the compiler), while the following tables contain only those entries where the settings that have been tested make a difference (this has to be considered when reading the total values at the bottom of each table). The PowerPC was chosen as target architecture because it is best supported by vbcc (as the optimizations discussed here are done in a machine-independant way, similar results can be expected for other architectures). There are very complex interactions between all the optimizations performed, and therefore side effects caused by other optimizations distort the results somewhat. Nevertheless, this approach seems more realistic than turning off all optimizations as a base for reference.

#### 3.3.1 Flow Optimizations

The basic data-structure most optimization algorithms operate on, is the control-flow graph. Its nodes represent pieces of code (usually basic blocks of intermediate code, sometimes machine instructions, etc.). The edges are possible flows of control.

Several optimizations working mainly on the control flow can be easily implemented and are done by many compilers. For example, code which is unreachable will be removed and branches to other branches or branches around branches will be simplified.

For example, the following code

```

void f(int x, int y)

{

if(x > y)

goto label1;

q();

label1:

goto label2;

r();

label2:

}

can be optimized to:

void f(int x, int y)

{

if(x <= y)

q();

}</pre>

```

Many different control flow optimizations have been implemented for many years, e.g. in [97]. Control flow analysis methods have been discussed for example in [5].

These optimizations usually eliminate unnecessary branch instructions and often enable additional optimizations. Therefore, they generally increase speed and reduce the size of the generated code. RAM space is not affected. That is why this kind of optimizations is suitable and recommended for small embedded systems. There are probably few or no specific considerations necessary for such systems.

vbcc always performs a series of control-flow optimizations when building a control flow graph. Also, several such transformations are spread over several optimization phases and are hard to remove. Therefore, no results are provided for the effect of those optimizations in vbcc.

#### 3.3.2 Dead Assignment Elimination

If a variable is assigned a value which is never used (either because it is overwritten or its lifetime ends), the assignment will be removed by this optimization. Although source code usually contains few dead assignments, this optimization is crucial to remove code which has become dead due to other optimizations.

For example, the following code

```

int x;

void f()

{

int y;

x = 1;

y = 2;

x = 3;

}

```

can be optimized to:

```

int x;

void f()

{

x = 3;

}

```